# ГОСУДАРСТВЕННЫЙ НАУЧНЫЙ ЦЕНТР РОССИЙСКОЙ ФЕДЕРАЦИИ ИНСТИТУТ ФИЗИКИ ВЫСОКИХ ЭНЕРГИЙ

ИФВЭ 2005–4 ОУ-У70

В.А. Коковин, В.В. Комаров

### КОНТРОЛЛЕР ТАЙМЕРНОЙ СЕТИ ОБЩЕЙ ТАЙМЕРНОЙ СИСТЕМЫ УСКОРИТЕЛЬНОГО КОМПЛЕКСА ИФВЭ

Направлено в "Приборы и системы. Управление, контроль, диагностика"

Протвино 2005

УДК 539.1.07:621.384.6 М-24

#### Аннотация

Коковин В.А., Комаров В.В. Контроллер таймерной сети общей таймерной системы ускорительного комплекса ИФВЭ: Препринт ИФВЭ 2005–4. – Протвино, 2005. – 9 с., 5 рис., 2 табл., библиогр.: 6.

Приведено функциональное описание модуля контроллера таймерной сети, который управляет потоками таймерной информации в общей таймерной системе ускорительного комплекса Института физики высоких энергий. Представлена реализация модуля в виде набора цифровых автоматов с конечным числом внутренних состояний. Рассмотрены особенности обработки параллельных потоков входной таймерной информации и коммутации этих потоков на глобальную и локальную магистрали таймерной сети. Приведены оценки пропускной способности каналов модуля и вероятности потерь таймерных сообщений. Обосновывается применение современных ПЛИС фирмы Altera в качестве элементной базы контроллера таймерной сети.

#### **Abstract**

Kokovin V.A., Komarov V.V. Timing Network Controller of IHEP Accelerators Complex General Timing System: IHEP Preprint 2005–4. – Protvino, 2005. – p. 9, fig. 5, tables 2, refs.: 6.

The paper describes the functionalities of the Timing Network Controller module directing the timing information flows in the General Timing System of the IHEP accelerators complex. The module realization has been presented as a set of the digital automatic devices with the finite number of the inner states. The peculiarities of both the processing of the parallel input timing information flows and the commutation of these flows to global and local buses of the Timing Network have been considered. The module channels capacity and probability of the timing messages losses have been estimated. The application of the modern Altera firm FPGA as a basic component for the Timing Network Controller module is well grounded.

#### **ВВЕДЕНИЕ**

Общая таймерная система У-70 (ОТС) предназначена для генерации и распределения между контроллерами оборудования таймерной информации, необходимой для выполнения задач контроля и управления в рамках системы управления ускорительного комплекса У-70 [1]. Новая реализация ОТС отличается наличием двух магистралей – глобальной кольцевой (ГКМ) и локальной радиальной (ЛРМ) [2], которые взаимодействуют между собой через генераторы таймерных сообщений. Ядром каждого из них является контроллер таймерной сети (КТС), управляющий потоками таймерной информации (ТИ) в соответствии с их приоритетами.

#### 1. КТС – КОММУТАТОР ПОТОКОВ ТИ

КТС представляет собой сложный цифровой автомат с конечным числом внутренних состояний. Он состоит из набора последовательных конечных автоматов, у которых множества входных сигналов не пересекаются. Главная задача КТС – обрабатывать входную ТИ и коммутировать её на выходах. Параллелизм обработки входной таймерной информации достигается за счёт независимой работы каждого конечного автомата.

КТС как коммутатор характеризуется числом входных и выходных потоков ТИ, временем реакции на обработку потоков и надёжностью работы. Особое внимание уделяется времени реакции, поскольку таймерные сообщения передают также и кодированную информацию об импульсах, используемых для синхронизации различных технологических процессов с требуемой точностью по времени.

Цифровые конечные автоматы целесообразно реализовать на программируемых логических интегральных схемах, которые предоставляют в распоряжение разработчика современный набор средств по проектированию и отладке сложных устройств и обеспечивают высокую надежность их работы. В частности, КТС выполнен на ПЛИС фирмы ALTERA (EP1K100TC208).

#### 1.1. Входные и выходные потоки ТИ

Под <u>входным потоком ТИ</u> (далее – входным потоком) понимается таймерная информация, подаваемая на входные порты КТС в любом из следующих форматов:

- кодированные таймерные сообщения (TC), соответствующие стандарту MIL1553 и поступающие из глобальной кольцевой магистрали, – поток IF<sub>1</sub>;

- внешние импульсы, синхронные с циклом ускорителя, поток IF<sub>2</sub>;

- программируемые TC из внешней памяти поток IF<sub>3</sub>.

Таким образом, на входы КТС поступают три независимых потока. Любой входной поток после обработки должен иметь возможность поступать на любой выходной канал.

<u>Выходные потоки ТИ</u> (далее – выходные потоки) более однородны и представляют собой кодированные ТС, поступающие на выходные каналы КТС в стандарте MIL1553. Определены два выходных потока:

- поток кольцевой магистрали OF<sub>1</sub>;

- поток радиальной магистрали OF<sub>2</sub>.

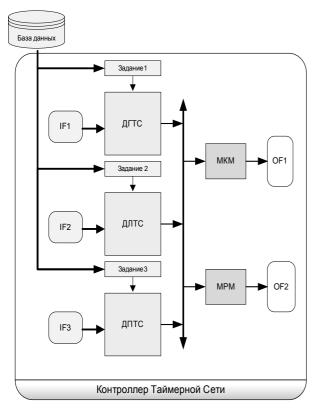

На рис. 1 показана упрощенная блок-схема обработки и прохождения потоков в КТС, где обозначены следующие блоки:

Рис.1 Упрощенная блок-схема КТС

ДГТС – диспетчер глобальных ТС;

ДЛТС – диспетчер локальных ТС;

ДПТС – диспетчер программируемых ТС;

МКМ – менеджер кольцевой магистрали;

МРМ – менеджер радиальной магистрали.

<u>Диспетчеры</u> обрабатывают свои входные потоки и осуществляют маршрутизацию ТС, записывая результат в буферную память соответствующего направления. В ТС не указывается адрес потребителя, поэтому маршрутизация потоков ТИ определяется только заданиями, которые заносятся в КТС из базы данных.

Менеджеры считывают информацию из буферной памяти и коммутируют потоки ТИ, подготавливая и направляя ТС в соответствующие магистрали.

Взаимодействие между диспетчерами и менеджерами реализуется посредством семафорного механизма. Таким образом, последовательное выполнение операций в диспетчерах и менеджерах приводит к образованию сквозных каналов передачи потоков ТИ от входа к выходу КТС.

#### 1.2. Обслуживание очередей потоков

Когда скорость поступления любого входного потока становится больше скорости его продвижения по любому выходу, возникают очереди. Кроме того, сумма входных потоков, каждый из которых имеет более низкую скорость, чем выходной поток, может также создавать очереди на выходах. Для разрешения этой проблемы КТС оснащен механизмом обслуживания очередей потоков, который является необходимым элементом для любого устройства, работающего по принципу коммутации потоков.

Обслуживание очередей потоков организовано следующим образом. Основную функцию в этом механизме выполняет буферная память типа FIFO в каждом из диспетчеров. Второй составляющей механизма обслуживания очередей является использование приоритета прохождения потоков, принятого по умолчанию. Например, входной поток  $IF_1$  имеет наивысший приоритет при прохождении в  $\Gamma$ KM и наименьший – в  $\Gamma$ FM. Обратная картина с потоком  $IF_3$ , который имеет наивысший приоритет при прохождении в  $\Gamma$ FM и наименьший – в  $\Gamma$ FM.

#### 1.3. Пропускная способность КТС

Как уже было отмечено выше, любой входной поток должен поступать на любой выходной канал. Физическая пропускная способность канала, обслуживающего локальную магистраль, жёстко задана и соответствует 10К ТС/с. Этот постоянный такт передачи ТС позволяет «привязывать» импульсы, распространяемые по ЛРМ, к одной временной шкале. При этом тактовые синхросигналы сопровождают каждое таймерное сообщение, включая и те, в которых не содержится таймерная информация. Физическая пропускная способность канала, посредством которого осуществляется ретрансляция ТИ по глобальной магистрали, определяется только возможностями МІL1553 и составляет не более 20К ТС/с.

Для оценки производительности (пропускной способности) КТС определим усредненные по времени максимальные значения входных потоков ТИ, исходя из разрядности кодов ТС (Приложение 1) и временных параметров цикла ускорительного комплекса:

- Максимальное число ТС в ГКМ ограничено восьмиразрядным кодом и составляет 256. Усредняя поток IF<sub>1</sub> по времени цикла ускорительного комплекса У-70 (около 10 с), получаем максимальное значение интенсивности потока  $\lambda_1 = 25.6$  TC/c.

- Максимальный поток внешних импульсов IF<sub>2</sub> определяется числом доступных входов (16 у каждого KTC) и коэффициентом повторяемости импульсов с тем же кодом (практически всегда равен 1). Усреднение по времени работы Бустера (которое не превышает 2 с в каждом цикле У-70) дает максимальное значение интенсивности потока λ<sub>2</sub> = 8 TC/c. Эта величина является наибольшей по сравнению с интенсивностью потоков IF<sub>2</sub> в других KTC.

- Максимальный входной поток TC из внешней памяти ограничен 11-разрядным кодом и не превышает 2048. Усредняя поток IF<sub>3</sub> по времени цикла ускорительного комплекса У-70 (около 10 c), получаем максимальное значение интенсивности потока  $\lambda_3 = 204.8$  TC/c.

В табл. 1 представлены полученные оценки потоков и приведены времена обслуживания, означающие максимальное время обработки входной таймерной информации для различных направлений потоков. В таблице указаны величины  $T_{\text{обсл}}$ , характерные для коммутации  $IF_1$  по магистралям ГКМ и ЛРМ, которые превышают значения  $T_{\text{обсл}}$  для всех других вариантов переключений потоков [2].

#### Таблица 1

| Поток                   | Интенсивность потока $\lambda$ , TC/c | Время об-<br>служивания $T_{\text{обсл}}$ , мкс |

|-------------------------|---------------------------------------|-------------------------------------------------|

| IF <sub>1</sub>         | 25.6                                  |                                                 |

| IF <sub>2</sub>         | 8                                     |                                                 |

| IF <sub>3</sub>         | 204.8                                 |                                                 |

| $IF_1 \rightarrow OF_1$ |                                       | 52,8                                            |

| $IF_1 \rightarrow OF_2$ |                                       | 152,3                                           |

Введём следующие параметры [3]:

т – число мест в очереди;

ρ – коэффициент загрузки выходного канала;

$P_{\text{пот}}$  – вероятность потерь ТИ;

Q – относительная пропускная способность каналов КТС;

Коэффициент загрузки р получается из выражения

$$\rho = \lambda T_{\text{обсл}}$$

.

Тогда вероятность потерь  $P_{\text{пот}}$  и относительную пропускную способность Q определим из выражений (1) и (2):

$$P_{\text{not}} = \rho^{m+1} (1 - \rho) / (1 - \rho^{m+2}), \tag{1}$$

$$Q = 1 - P_{\text{not}} = 1 \ \rho^{m+1} (1-\rho)/(1-\rho^{m+2}) \ . \tag{2}$$

При увеличении размера буфера памяти m уменьшается вероятность потерь и увеличивается относительная пропускная способность Q KTC. Однако увеличение размера очереди приводит к большой задержке конкретных TC, что снижает их достоверность. Примем размер буфера FIFO на 8 TC (m=8), исходя из требований к ОТС со стороны технологического оборудования У-70 и физической пропускной способности каналов, обслуживающих глобальную и локальную магистрали.

При заданных параметрах  $\lambda_i$ ,  $T_{\text{обсл}}$  и m получим  $P_{\text{пот}}$  и Q. Для простоты расчёта примем, что входные потоки представляют собой <u>стационарные пуассоновские потоки</u> с интенсивностью  $\lambda$  [3]. Такое допущение позволит легко найти суперпозицию всех входных потоков методом простого сложения:

$$\begin{split} \lambda_{\scriptscriptstyle T} &= \lambda_1 + \, \lambda_2 + \, \lambda_3 < 25,6 \ TC/c, \\ \lambda_{\scriptscriptstyle \Pi} &= \lambda_1 + \, \lambda_2 + \, \lambda_3 < 204,8 \ TC/c. \end{split}$$

Получившиеся результаты  $P_{\text{пот}}$  и Q по каждому выходному каналу КТС сведены в табл. 2.

#### Таблица 2

| Выходной канал | Вероят-<br>ность<br>потерь,<br>Р <sub>пот</sub> | Относит.<br>пропускная<br>способность,<br>Q |  |  |  |

|----------------|-------------------------------------------------|---------------------------------------------|--|--|--|

| в ГКМ          | 1,05*10 <sup>-27</sup>                          | ~1                                          |  |  |  |

| в ЛРМ          | 9,54*10 <sup>-27</sup>                          | ~1                                          |  |  |  |

Введение приоритета при коммутации потоков обеспечивает гарантированно минимальную задержку высокоприоритетных TC. Например, перевод входного потока  $IF_1$  в выходной поток  $OF_1$  или перевод входного потока  $IF_3$  в выходной поток  $OF_2$  происходит с детерминированными систематическими задержками 13.8 мкс или 52.8 мкс соответственно [2], что определяется только временем обслуживания  $T_{oбсл}$ .

#### 2. ОБРАБОТКА ВХОДНЫХ ПОТОКОВ ТИ

Обработку входных потоков таймерной информации и маршрутизацию потоков в КТС осуществляют диспетчеры таймерных сообщений: ДГТС, ДЛТС и ДПТС. Каждый диспетчер представляет собой цифровой синхронный конечный автомат. Все цифровые конечные автоматы по законам функционирования условно делятся на два типа: конечный автомат Мили [4] и конечный автомат Мура [5]. Законы функционирования автоматов можно аналитически описать следующими выражениями:

$$q_{t+1} = \varphi(q_t, x_t), \tag{3}$$

$$\mathbf{w}_{t} = \mathbf{\psi} (\mathbf{q}_{t}, \mathbf{x}_{t}), \tag{4}$$

где  $q_t$ ,  $x_t$  — состояние и набор входных сигналов автомата в момент времени t;  $\phi$  — функция переходов, определяющая последующее внутреннее состояние автомата;  $\psi$  — функция выходов;  $w_t$  — выходной набор сигналов. Выражения (3) и (4) определяют автомат Мили. Особенность автомата Мура заключается в том, что выходной набор сигналов в выражении (4) зависит только от внутреннего состояния  $q_t$  и не зависит от входного набора сигналов.

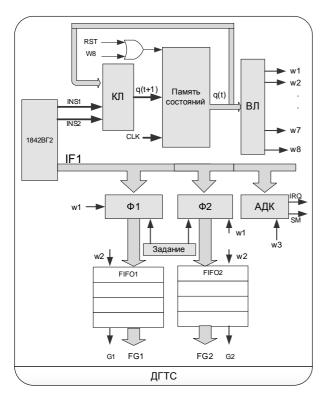

Рис.2. Функциональная схема ДГТС

## 2.1. Диспетчер глобальных таймерных сообшений

Диспетчер глобальных таймерных сообщений является последовательным синхронным конечным автоматом Мура (рис. 2).

Собственно сам конечный автомат состоит из трёх основных блоков:  $K\Pi$  – комбинационная логика на входе, которая формирует сигналы возбуждения автомата, память внутренних состояний и  $B\Pi$  – выходная логика, формирующая выходные сигналы  $w_t$ . Кроме того, ДГТС содержит:

- Фильтры (Ф1, Ф2) для маршрутизации входного потока IF<sub>1</sub>. Каждый фильтр, основанный на цифровом компараторе, настраивается на выбранные таймерные сообщения посредством задания, записанного в регистр.

- Два FIFO, которые являются составной частью механизма обслуживания очередей.

- Блок АДК, анализирующий дополнительный код (Приложение 2) и выдающий сигнал запроса прерывания IRQ на

системную шину Multibus-1 генератора таймерных сообщений и сигнал SM запуска внешней памяти.

В исходном состоянии  $q_t = q_0$ , и множество выходных сигналов  $w_0$  находится в неактивном состоянии. В это состояние диспетчер переходит, если сигналы W8 или RST становятся активными. После того, как декодер TC (1842ВГ2) примет командное слово, на его управляющих выводах появится активный сигнал INS1, а после приема слова данных – сигнал INS2. Появление этих сигналов возбуждает конечный автомат и означает, что TC поступило на входы фильтров  $\Phi$ 1 и  $\Phi$ 2 диспетчера.

При последовательной смене внутренних состояний  $q_t$  синхронно с тактом СLK (12 МГц), на выходе автомата формируются наборы выходных сигналов  $w_t$ , которые осуществляют следующие операции:

- сравнение кода события (Приложение 1) в фильтрах;

- запись таймерного сообщения в FIFO;

- формирование в АДК запроса прерывания IRQ, если TC содержит признак прерывания;

- формирование в АДК сигнала старта внешней памяти SM, если TC содержит признак запуска памяти;

- сброс конечного автомата в исходное состояние.

Все ТС, поступающие в FIFO1, формируют на выходе ДГТС поток FG1, который имеет высший приоритет, а таймерные сообщения, поступающие в FIFO2, формируют на выходе ДГТС поток FG2, который имеет самый низкий приоритет.

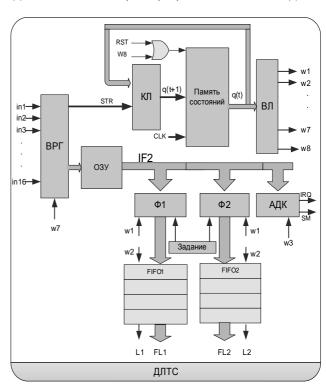

#### 2.2. Диспетчер локальных таймерных сообщений

Таймерная информация поступает на ДЛТС в виде внешних импульсов, для обработки которых диспетчер ДЛТС дополняется входным регистром ВРГ и ОЗУ (рис. 3). Перед началом очередного цикла ускорителя в ОЗУ записываются данные с кодами ТС, при этом каждый номер ячейки ОЗУ жестко соответствует номеру входного канала IN1, IN2,...,IN16. Любой входной

сигнал, пришедший на вход ДЛТС, взводит свой независимый триггер ВРГ. В результате формируются адрес ячейки ОЗУ и сигнал STR, а автомат переходит в состояние, отличное от исходного. При смене состояний конечного автомата  $q_t$  с частотой 12 МГц выполняются следующие операции:

- сравнение кода события в фильтрах;

- запись таймерного сообщения в FIFO;

- формирование в АДК запроса прерывания IRQ, если ТС содержит признак прерывания;

- формирование в АДК сигнала старта внешней памяти SM, если ТС содержит признак запуска памяти;

- сброс взведенного триггера в ВРГ;

- сброс конечного автомата в исходное состояние.

Таким образом, работа автомата ДЛТС отличается от работы автомата ДГТС только наличием операции сброса взведенного триггера в ВРГ.

Рис.3. Функциональная схема ДЛТС

Таймерные сообщения, поступающие в FIFO1 и FIFO2, формируют на выходе ДЛТС потоки FL1 и FL2 соответственно, каждый из которых имеет второй по уровню приоритет.

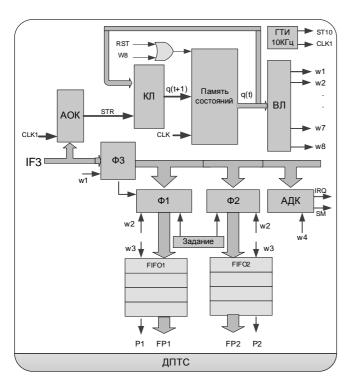

#### 2.3. Диспетчер программируемых таймерных сообщений

Работа ДПТС синхронизируется генератором тактовых импульсов (ГТИ) с частотой 10 КГц. Функциональная схема ДПТС представлена на рис. 4. По сигналу СLК1 в АОК (анализатор основного кода) происходит анализ основного кода (Приложение 1) очередного слова команды ТС, поступившего из внешней памяти. Если в основном коде содержится хотя бы один бит с логической единицей, то АОК вырабатывает сигнал STR для изменения состояния конечного автомата в ДПТС. Цифровой фильтр  $\Phi$ 3 не пропускает «пустые» ТС потока  $\Gamma$ 3, у которых основной код равен нулю, в буферную память.

При смене состояний конечного автомата выполняются следующие операции:

- анализ основного кода в фильтре ФЗ;

- сравнение кода события и основного кода в фильтрах Ф1 и Ф2;

- запись таймерного сообщения в FIFO;

- формирование в АДК запроса прерывания IRQ, если TC содержит признак прерывания;

- формирование в АДК сигнала старта внешней памяти SM, если TC содержит признак запуска памяти;

- сброс конечного автомата в исходное состояние.

Рис.4. Функциональная схема ДПТС

Таким образом, по операциям, управляемыми автоматами, ДПТС и ДГТС не отличаются друг от друга. Кроме блоков, указанных в начале параграфа, остальные блоки в ДПТС выполняют те же функции, что и в предыдущих диспетчерах.

Все таймерные сообщения, поступающие в FIFO2, формируют на выходе ДПТС поток FP2, который имеет высший приоритет, а таймерные сообщения, поступающие в FIFO1, формируют на выходе ДПТС поток FP1, который имеет самый низкий приоритет.

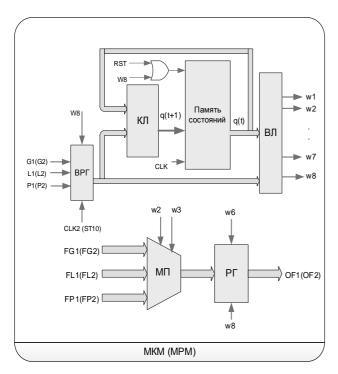

### 3. ФОРМИРОВАНИЕ ВЫХОДНЫХ ПОТОКОВ ТС

Как уже упоминалось выше, формированием выходных потоков ТС и коммутацией потоков (в отличие от диспетчеров, которые выполняют маршрутизацию потоков) занимаются выходные менеджеры МКМ и МРМ. Семафорный механизм взаимодействия диспетчеров и менеджеров определяет статус менеджеров, как подчиненных синхронных ко-

нечных автоматов Мили, поскольку изменение состояний последних происходит только при активации их автоматами диспетчеров.

На рис. 5 представлена функциональная схема МКМ (MPM). Как видно из схемы, в формировании наборов выходных сигналов  $w_t$  участвуют как сигналы текущего состояния автомата  $q_t$ , так и входные сигналы G, L и P, поступающие из соответствующих диспетчеров. Эти сигна-

лы являются флагами семафорного механизма, которые взводятся при заполнении FIFO и остаются в этом состоянии до полной очистки памяти.

Очередность прохождения выходных потоков диспетчеров FG1 (FG2), FL1 (FL2) и FP1 (FP2) через мультиплексор потоков МП определяется кодовой комбинацией сигналов w2 и w3. При формировании выходных сигналов  $w_t$  в выходной логике ВЛ учитывается жёстко заданный приоритет прохождения потоков.

Тактовый сигнал СLK2 (1МГц) определяет частоту обновления данных на выходах регистра ВРГ. Поскольку импульсы СLK следуют с частотой 12 МГц, то смена всех состояний автомата успевает закончиться до прихода очередного такта СLK2. Функциональная схема MPM отлича-

Рис.5.Функциональная схема МКМ и МРМ

ется от схемы МКМ только тем, что вместо тактового сигнала СLK2 на входе ВРГ используется серия тактовых импульсов ST10 (10 КГц), получаемая от генератора ГТИ диспетчера программируемых таймерных сообщений. Введение этого сигнала позволяет организовать процесс передачи ТС в локальную радиальную магистраль независимо от наличия таймерной информации в ТС.

Ниже описаны действия при смене состояний автоматов:

- чтение из буферной памяти (FIFO) диспетчеров (согласно заданному приоритету);

- управление мультиплексором;

- запись таймерного сообщения в выходной регистр РГ;

- сброс конечного автомата и регистров ВРГ и РГ в исходное состояние.

Таким образом, при каждом цикле работы автоматов выполняется коммутация входных потоков, другими словами, формируется сквозной канал передачи ТС из

памяти диспетчеров в выходные регистры менеджеров. Поскольку все диспетчеры содержат по два FIFO, каждое из которых жестко связано со «своим» менеджером, то оба менеджера работают независимо друг от друга.

#### **ЗАКЛЮЧЕНИЕ**

Успешная работа КТС в составе аппаратуры общей таймерной системы на ускорителе У-70 подтвердила правильность выбора архитектуры модуля [2]. Построение подобного модуля с использованием технологии конечных автоматов при небольшом числе внутренних состояний имеет преимущество перед микропроцессорной реализацией. С одной стороны, микропроцессор представляет собой сложный автомат, смена состояний которого определяется выполняемой программой. Большое число его состояний и переходов между ними, а также асинхронная работа микропроцессора уменьшают надежность функционирования устройства и не гарантируют своевременной доставки таймерной информации. С другой стороны, реализация КТС в виде набора конечных синхронных автоматов позволяет организовать обработку параллельных потоков таймерной информации в режиме реального времени и обеспечить строго детерминированную задержку при доставке информации к пунктам назначения.

Применение в качестве элементной базы ПЛИС даёт возможность уменьшить затраты при разработке, выполнить редакцию законченного проекта на той же печатной плате модуля, изменить или добавить те или иные свойства КТС, продиктованные практикой. За счет этих возможностей существенно снижается конечная стоимость модуля на базе ПЛИС. Следует также отметить, что внутренние структуры макроячеек ПЛИС максимально подходят для построения одноуровневых и многоуровневых цифровых конечных автоматов. Кроме того, ПЛИС обеспечивает как низкое энергопотребление, так и высокую надежность построенных на ее основе сложных многоэлементных модулей [6].

В заключение авторы выражают свою искреннюю благодарность научному сотруднику  $\Gamma$ .М.Антоничеву за участие в отладке КТС при внедрении новой общей таймерной системы на ускорительном комплексе ИФВЭ.

#### Список литературы

- [1] Балакин С.И. и др. Новая система управления ускорительного комплекса У-70 (статус). XVIII конференция по ускорителям заряженных частиц RUPAC-2002 (сб. докладов). Обнинск, 2002, т.2, с.603-608.

- [2] Комаров В.В. Базовые принципы построения общей таймерной системы ускорительного комплекса У-70: Препринт ИФВЭ 2004-46. Протвино, 2004.

- [3] Вентцель Е.С. Теория вероятностей. М.: Высшая школа, 1999.

- [4] Mealy G.H. A method for synthesizing sequential circuits. // Bell System Techn. J. Vol. 34. 1955. P. 1045–1079.

- [5] Moore E.F. Gedanhen-experiments on sequential machines. // In C. Shannon and J. McCarthy editors. Automata Studies Princeton University Press. 1956. P. 129–153.

- [6] Соловьев В.В. Структурные модели конечных автоматов при их реализации на ПЛИС. // Chip News. Инженерная микроэлектроника. 2002. № 9. С. 4–14.

Рукопись поступила 25 марта 2005 г.

#### Формат слова команды таймерного сообщения

| Код адреса    |    |    |    | Код импульса |              |    |    |    |    | Код события |    |    |    |    |    |

|---------------|----|----|----|--------------|--------------|----|----|----|----|-------------|----|----|----|----|----|

| 15            | 14 | 13 | 12 | 11           | 10           | 09 | 08 | 07 | 06 | 05          | 04 | 03 | 02 | 01 | 00 |

| 0             | 0  | 0  | 0  | 0            | X            | X  | X  | X  | X  | X           | X  | X  | X  | X  | X  |

| Глобальные ТС |    |    |    |              |              |    |    |    |    | <b></b>     |    |    |    |    |    |

|               |    |    |    |              | Локальные ТС |    |    |    |    |             |    |    |    |    |    |

Коды события и импульса [2] составляют основной код таймерного сообщения (ТС). По глобальной кольцевой магистрали распространяются только те ТС, которые переносят информацию о событиях. Код события всегда сопровождается кодом импульса, чтобы иметь возможность непосредственно синхронизировать процессы с минимальной аппаратной задержкой, исключая неопределенное время реакции на обработку событийного прерывания. Таким образом, глобальное ТС занимает 8 разрядов слова команды.

По локальной радиальной магистрали распространяются как события, так и полный набор импульсов, определяемые основным кодом ТС. Таким образом, локальное ТС занимает 11 разрядов.

Код адреса в ЛРМ всегда равен нулю, а в ГКМ адресное поле слова команды может использоваться для дополнительного кода, сопровождающего определенное ТС.

#### приложение 2

#### Функции дополнительного кода

|                    | Код Адреса |    |    |    |  |  |  |  |

|--------------------|------------|----|----|----|--|--|--|--|

| 15                 | 14         | 13 | 12 | 11 |  |  |  |  |

| IRQ                | M3         | M2 | M1 | •  |  |  |  |  |

| Дополнительный Код |            |    |    |    |  |  |  |  |

Для того чтобы сформировать в КТС сигнал IRQ или запустить процесс чтения внешней памяти от определенного ТС, в адресное поле данного ТС записывается соответствующий дополнительный код, содержащий признак выполняемого действия или набор признаков выполняемых действий. Значения бит дополнительного кода в состоянии логической единицы:

**IRQ** – запрос прерывания, подаваемый на системную шину Multibus-1;

М3 – запуск памяти в ГТС №3;

М2 – запуск памяти в ГТС №2;

М1 – запуск памяти в ГТС №1.

Дополнительный код, записанный вместе с основным кодом в памяти ДЛТС или внешней памяти одного из генераторов таймерных сообщений, может быть использован как в этом же КТС, так и передан другим КТС по глобальной магистрали. Если ТС, сопровождаемое дополнительным кодом, передается в локальную магистраль, то дополнительный код автоматически стирается.

В.А Коковин., В.В. Комаров.

Контроллер таймерной сети общей таймерной системы ускорительного комплекса ИФВЭ.

Оригинал-макет подготовлен с помощью системы Word.

Редактор Н.В. Ежела.

Подписано к печати 28.03.2005. Формат  $60 \times 84/8$ . Офсетная печать. Печ.л. 1, 37. Уч. – изд.л. 1,1. Тираж 130. Заказ 29. Индекс 3649. ЛР №020498 от 17.04.97.

ГНЦ РФ Институт физики высоких энергий, 142282, Протвино Московской обл.

Индекс 3649

ПРЕПРИНТ 2005-4, ИФВЭ, 2005